A | B | C | D | E | F | G | H | CH | I | J | K | L | M | N | O | P | Q | R | S | T | U | V | W | X | Y | Z | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9

A Z80 manufactured in June 1976 according to the date stamp | |

| General information | |

|---|---|

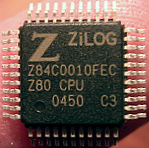

| Launched | July 1976 |

| Discontinued | June 2024 |

| Marketed by | Zilog |

| Designed by | Federico Faggin, Masatoshi Shima |

| Common manufacturer | |

| Performance | |

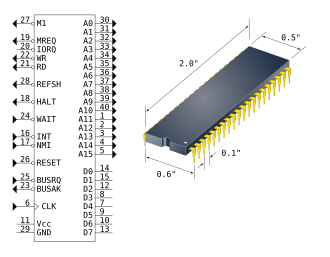

| Max. CPU clock rate | 2.5 MHz to 8 MHz[b] |

| Data width | 8 bits[1] |

| Address width | 16 bits[1] |

| Architecture and classification | |

| Application | Embedded, desktop, handheld |

| Technology node | 4 μm process |

| Instruction set | Z80[c] |

| Physical specifications | |

| Transistors |

|

| Packages | |

| History | |

| Predecessor | Intel 8080 |

| Successors | |

The Zilog Z80 is an 8-bit microprocessor designed by Zilog that played an important role in the evolution of early computing. Software-compatible with the Intel 8080, it offered a compelling alternative due to its better integration and increased performance. The Z80 boasted fourteen registers compared to the 8080's seven, along with additional instructions for bit manipulation, making it a more powerful chip.

Initially intended for use in embedded systems like the 8080, the Z80's combination of compatibility, affordability, and superior performance propelled it to widespread adoption in video game systems and home computers during the late 1970s and early 1980s, fueling the personal computing revolution.

The Z80 was the brainchild of Federico Faggin, a key figure behind the creation of the Intel 8080. After leaving Intel in 1974, Faggin co-founded Zilog with Masatoshi Shima. The Z80 was released in July 1976. With the revenue from the Z80, the company built its own chip factories.[2] Zilog licensed the Z80 to the US-based Synertek and Mostek, which had helped them with initial production, as well as to a European second-source manufacturer SGS. The design was also copied by several Japanese, Eastern European and Soviet manufacturers.[d] This won the Z80 acceptance in the world market since large companies like NEC, Toshiba, Sharp, and Hitachi started to manufacture the device (or their own Z80-compatible clones or designs).

The Z80 continued to be used in embedded systems for decades after its introduction, with ongoing advancements. The latest addition to the Z80 family is the eZ80, which is offered alongside successor chips. Zilog announced the discontinuation of the Z80 in April 2024 after nearly five decades of production.

History

Early history

At Fairchild Semiconductor, and later at Intel, physicist and engineer Federico Faggin had been working on fundamental transistor and semiconductor manufacturing technology. He also developed the basic design methodology used for memories and microprocessors at Intel and led the work on the Intel 4004, the Intel 8080 and several other ICs. Masatoshi Shima was the principal logic and transistor-level designer of the 4004 and the 8080 under Faggin's supervision, while Ralph Ungermann was in charge of custom integrated circuit design.[3]

In early 1974, Intel viewed their microprocessors not so much as products to be sold on their own but as a way to sell more of their main products, static RAM and ROM. A reorganization placed many of the formerly independent sections under the direction of Les Vadasz, further diluting the microprocessor's place in the company. That year, the 1973–1975 recession reached a peak and Intel laid off a number of employees.[3] All of this led to Faggin becoming restless, and he invited Ungermann out for drinks and asked if he would be interested in starting their own company. Ungermann immediately agreed, and as he had less to do at Intel, left in August or September, followed by Faggin, whose last day at Intel was Halloween 1974.[4] When Shima heard, he asked to come to the new company as well, but having no actual product design or money, they told him to wait.[5]

The newly formed and unnamed company initially began designing a single-chip microcontroller called the 2001. They met with Synertek to discuss fabrication on their lines, and when Faggin began to understand the costs involved it became clear that a low-cost product like this would not be able to compete with a design from a company with its own production lines, like Intel. They then began considering a more complex microprocessor instead, initially known as the Super 80, with the main feature being its use of a +5 V bus[5] instead of the more common −5, +5 and 12 V used by designs like the 8080. The new design was intended to be compatible with the 8080, but add many of the nice features of the Motorola 6800, including index registers and improved interrupts.[6]

Exxon investment, detailed development begins

While still being set up, the industry newsletter Electronic News heard of them and published a story on the newly formed company. This attracted the attention of Exxon Enterprises, Exxon's high-tech investment arm. At the time, in the midst of the recession, there was very little venture capital available, with a total of $10 million for the entire industry being spent in all of 1975 (equivalent to $57 million in 2023). Someone from Exxon contacted the still-unnamed company,[5] and arranged a meeting that eventually led to them providing an initial $500,000 funding in June 1975 (equivalent to $2.8 million in 2023).[7]

With funding being discussed, and a design to be built, Shima joined in February 1975.[6] Shima immediately set about producing a high-level design, adding several concepts of his own. In particular, he used his experience on NEC minicomputers to add the concept of two sets of processor registers so they could quickly respond to interrupts.[4][e] Ungerman began the development of a series of related controllers and peripheral chips that would complement the design.[8]

Through this period, Shima developed a legendary reputation for being able to convert logic concepts into physical design in realtime; while discussing a proposed feature, he would often interrupt and state how much room that would take on the chip and veto its addition if it was too large.[9] The first pass at the design was complete by April 1975. Shima had completed a logic layout by the beginning of May. A second version of the logic design was issued on August 7 and the bus details by September 16. Tape-out was completed in November and converting the tape into a production mask required two more months.[10]

Faggin had already started looking for a production partner. By this time, Synertek and Mostek had both set up the depletion-mode production lines that could be used to produce the design. Having talked to Synertek previously, Faggin approached them first. However, the president of Synertek demanded that the company be given a second source license, allowing them to sell the design directly. Faggin thought this would mean they could never compete even if they set up their own lines, and the agreement fell through. He then turned to Mostek, who agreed to a term of exclusivity while Zilog got their lines set up, and were eventually given the second source agreement.[11]

After considering many names for the new company, and finding them so unmemorable they could not recall them even a day later, Faggin and Ungermann were kicking around ideas based on "integrated logic" when Ungermann said "how about Zilog?" Faggin immediately agreed, stating they could say it was the "last word in integrated logic". When they met the next day and both immediately recalled it, the company had its name.[12]

Into production

The first samples were returned from Mostek on March 9, 1976.[8] By the end of the month, they had also completed an assembler-based development system. Some of the Z80 support and peripheral ICs were under development at this point, and many of them were launched during the following year. Among them were the Z80 CTC (counter/timer), Z80 DMA[13] (direct memory access), Z80 DART (dual asynchronous receiver–transmitter), Z80 SIO (synchronous communication controller), and Z80 PIO (parallel input/output).

The Z80 was officially launched in July 1976.[14] One of the first customers was a buyer who, unknown to Zilog, worked for NEC. At the time, the Japanese electronics companies were well known for taking US chip designs and producing them without a license. The Zilog team had worried about this, and Faggin had come up with the idea of adding transistors that would be subtly modified to operate differently than a visual inspection would suggest. Shima added six of these "traps" around the design. Sometime later, Shima was told by an engineer within NEC that the traps had delayed their copying efforts by six months.[15]

The successful launch allowed Faggin and Ungermann to approach Exxon looking for funding to build their own fab. The company agreed, and Zilog built a production line very rapidly. This allowed them to capture about 60 to 70% of the total market for Z80 sales.[16] With their own line running, Mostek was given the go-ahead to start sales of their own versions, the MK3880, which provided a second-source for customers which Intel lacked. At the time, a second-source was considered extremely important as a start-up like Zilog might go out of business and leave potential customers stranded.[6][f]

Comparison with the 8080

Faggin designed the instruction set to be binary compatible with the 8080[17][18] so that most 8080 code, notably the CP/M operating system and Intel's PL/M compiler for 8080 (as well as its generated code), would run unmodified on the new Z80 CPU. Masatoshi Shima designed most of the microarchitecture as well as the gate and transistor levels of the Z80 CPU, assisted by a small number of engineers and layout people.[19][20] CEO Federico Faggin was actually heavily involved in the chip layout work, together with two dedicated layout people. According to Faggin, he worked 80 hours a week in order to meet the tight schedule given by the financial investors.[2]

The Z80 offered many improvements over the 8080:[18]

- An enhanced instruction set including:

- a more logical, comprehensible and readable system of assembler instruction mnemonics

- more flexible 16-bit data movement (load, or LD) instructions, crucially including the stack pointer SP

- more flexible addressing modes for input/output to external peripheral ports

- single-bit addressing of all registers and memory, including bit testing

- shifts/rotates on memory and registers other than the accumulator

- improved and more accurate (than the previous 8080) BCD arithmetic

- rotate instructions for BCD number strings in memory

- 16-bit subtraction and 8-bit negation

- program looping

- program counter (PC) relative jumps

- block copy, block input/output (I/O), and byte search instructions.[21]

- An overflow flag with better support for signed 8- and 16-bit arithmetics.[g]

- New IX and IY index registers with instructions for direct base+offset addressing

- A better interrupt system:

- A more automatic and general vectorized interrupt system, mode 2, primarily intended for Zilog's line of counter/timers, DMA and communications controllers, as well as a fixed vector interrupt system, mode 1, for simple systems with minimal hardware (with mode 0 being the 8080-compatible mode).[22]

- A non-maskable interrupt (NMI), which can be used to respond to power-down situations or other high-priority events (and allowing a minimalistic Z80 system to easily implement a two-level interrupt scheme in mode 1).

- A complete duplicate register file,[23] which could be quickly switched, to speed up response to interrupts such as fast asynchronous event handlers or a multitasking dispatcher. Although they were not intended as extra registers for general code, they were nevertheless used that way in some applications.[h]

- Less hardware required for power supply, clock generation and interface to memory and I/O

- Single 5-volt power supply (the 8080 needed −5 V, +5 V, and +12 V).

- Single-phase 5-volt clock (the 8080 needed a high-amplitude (9 to 12 volts) non-overlapping two-phase clock).

- Built-in DRAM refresh, which would otherwise require external circuitry, unless SRAM, more expensive and less dense (but faster), was used.[i]

- Non-multiplexed buses (the 8080 had state signals multiplexed onto the data bus).

- A special reset that zeroes only the program counter, so that a single Z80 CPU could be used in a development system such as an in-circuit emulator.[24]

Success in the market

The Z80 took over from the 8080 and its offspring, the 8085, in the processor market[25] and became one of the most popular and widely used 8-bit CPUs.[26][27] Some organizations such as British Telecom remained loyal to the 8085 for embedded applications, owing to their familiarity with it and to its on-chip serial interface and interrupt architecture. Likewise, Zenith Data Systems paired the 8085 with the 16-bit Intel 8088 in its first MS-DOS computer, the Zenith Z-100, despite having previous experience with its pioneering Z80-based Heathkit H89 and Zenith Z-89 products. However, other computers were made integrating the Z80 with other CPUs: the Radio Shack TRS-80 Model 16 with a Motorola 68000, the DEC Rainbow with an 8088, and the Commodore 128 with a MOS Technology 8502.

Zilog was later producing a low-power Z80 suitable for the growing laptop computer market of the early 1980s. Intel produced a CMOS 8085 (80C85) used in battery-powered portable computers, such as the Kyocera-designed laptop from April 1983, also sold by Tandy (as TRS-80 Model 100), Olivetti, and NEC. In following years, however, CMOS versions of the Z80 (from both Zilog and Japanese manufacturers) would dominate this market as well, in products such as the Amstrad NC100, Cambridge Z88 and Tandy's own WP-2.

Perhaps a key to the initial success of the Z80 was the built-in DRAM refresh, at least in markets such as CP/M and other office and home computers. (Most Z80 embedded systems use static RAM that do not need refresh.) It may also have been its minimalistic two-level interrupt system, or conversely, its general multi-level daisy-chain interrupt system useful in servicing multiple Z80 IO chips. These features allowed systems to be built with less support hardware and simpler circuit board layouts.

However, others claim that its popularity was due to the duplicated registers that allowed fast context switches or more efficient processing of things like floating-point math compared to 8-bit CPUs with fewer registers. (The Z80 can keep several such numbers internally, using HL'HL, DE'DE and BC'BC as 32-bits registers, avoiding having to access them from slower RAM during computation.)[28]

For the original NMOS design, the specified upper clock-frequency limit increased successively from the introductory 2.5 MHz, via the well known 4 MHz (Z80A), up to 6 MHz (Z80B) and 8 MHz (Z80H).[29][30] The NMOS version has been produced as a 10 MHz part since the late 1980s. CMOS versions were developed with specified upper frequency limits ranging from 4 MHz up to 20 MHz for the version sold today. The CMOS versions allowed low-power standby with internal state retained, having no lower frequency limit.[j] The fully compatible derivatives HD64180/Z180[31][32] and eZ80 are currently specified for up to 33 MHz and 50 MHz, respectively.

Design

Programming model and register set

The programming model and register set of the Z80 are fairly conventional, ultimately based on the register structure of the Datapoint 2200. The Z80 was designed as an extension of the Intel 8080, created by the same engineers, which in turn was an extension of the 8008. The 8008 was basically a PMOS implementation of the TTL-based CPU of the Datapoint 2200.[k]

The 2200 design allowed 8-bit registers H and L (High and Low) to be paired into a 16-bit address register HL.[l] In the 8080, this pairing was added to the BC and DE pairs as well, while HL was generalized to allow use as a 16-bit accumulator, not just an address register. The 8080 also introduced immediate 16-bit data for BC, DE, HL, and SP loads. Furthermore, direct 16-bit copying between HL and memory was now possible, using a direct address.

The Z80 orthogonalized this further by making all 16-bit register pairs, including IX and IY, more general purpose, as well as allowing 16-bit copying directly to and from memory for all of these pairs. The 16-bit IX and IY registers in the Z80 are primarily intended as base address-registers, where a particular instruction supplies a constant offset that is added to the previous values, but they are also usable as 16-bit accumulators, among other things. A limitation is that all operand references involving IX or IY require an extra instruction prefix byte, adding at least four clock cycles over the timing of an instruction using HL instead; this sometimes makes using IX or IY less efficient than a method using only the 8080-model registers. The Z80 also introduced a new signed overflow flag and complemented the fairly simple 16-bit arithmetics of the 8080 with dedicated instructions for signed 16-bit arithmetics.

The 8080-compatible registers AF, BC, DE, HL are duplicated as a separate register file in the Z80,[34] where the processor can quickly (four t-states, the least possible execution time for any Z80 instruction) switch from one bank to the other;[35] a feature useful for speeding up responses to single-level, high-priority interrupts. A similar feature was present in the 2200, but was never implemented at Intel. The dual register-set is very useful in the embedded role, as it improves interrupt handling performance, but found widespread use in the personal computer role as an additional set of general registers for complex code like floating-point arithmetic or home computer games.

The duplicate register file is often referred to as the "alternate register set" (by some, the "primed" register file since the apostrophe character is used to denote them in assembler source code and the Zilog documentation). This emphasizes that only one set is addressable at any time. However, the 8-bit accumulator A with its flag register F is bifurcated from the "general purpose" register pairs HL, DE and BC. This is accomplished with two separate instructions used to swap their accessibilities: EX AF,AF' exchanges only register pair AF with AF', while the EXX instruction exchanges the three general purpose register pairs HL, DE and BC with their alternates HL', DE' and BC'. Thus the accumulator A can interact independently with any of the general purpose 8-bit registers in the alternate (or primed) register file, or, if HL' contains a pointer to memory, some byte there (DE' and BC' can also transfer 8-bit data between memory and accumulator A).

This can become confusing for programmers because after executing EX AF,AF' or EXX what were previously the alternate (primed) registers are now the main registers, and vice versa. The only way for the programmer to tell which set(s) are in context (while "playing computer" while scrutinizing the assembler source text, or worse, poring over code with a debugger) is to trace where each register swap is made at each point in the program. Obviously if many jump and calls are made within these code segments it can quickly become difficult to tell which register file is in context unless carefully commented. Thus it is advisable that exchange instructions be used directly and in short discrete code segments. The Zilog Z280 instruction set includes JAF and JAR instructions which jump to a destination address if the alternate registers are in context (thus officially recognizing this programming complication).

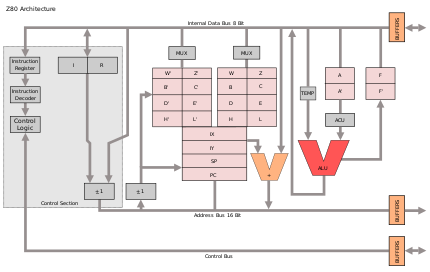

Registers

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

As on the 8080, 8-bit registers are typically paired to provide 16-bit versions. The 8080 compatible registers[36] are:

AF: 8-bit accumulator (A) and flag bits (F) carry, zero, minus, parity/overflow, half-carry (used for BCD), and an Add/Subtract flag (usually called N) also for BCDBC: 16-bit data/address register or two 8-bit registersDE: 16-bit data/address register or two 8-bit registersHL: 16-bit accumulator/address register or two 8-bit registersSP: stack pointer, 16 bitsPC: program counter, 16 bits

The new registers introduced with the Z80 are:

IX: 16-bit index or base register for 8-bit immediate offsetsIY: 16-bit index or base register for 8-bit immediate offsetsI: interrupt vector base register, 8 bitsR: DRAM refresh counter, 8 bits (msb does not count)AF': alternate (or shadow) accumulator and flags (toggled in and out with EX AF,AF' )BC',DE'andHL': alternate (or shadow) registers (toggled in and out with EXX)- Four bits of interrupt status and interrupt mode status

The refresh register, R, increments each time the CPU fetches an opcode (or an opcode prefix, which internally executes like a 1-byte instruction) and has no simple relationship with program execution. This has sometimes been used to generate pseudorandom numbers in games, and also in software protection schemes.[citation needed] It has also been employed as a "hardware" counter in some designs; an example of this is the ZX81, which lets it keep track of character positions on the TV screen by triggering an interrupt at wrap around (by connecting INT to A6).

The interrupt vector register, I, is used for the Z80 specific mode 2 interrupts (selected by the IM 2 instruction). It supplies the high byte of the base address for a 128-entry table of service routine addresses which are selected via an index sent to the CPU during an interrupt acknowledge cycle; this index is simply the low byte part of the pointer to the tabulated indirect address pointing to the service routine.[22] The pointer identifies a particular peripheral chip or peripheral function or event, where the chips are normally connected in a so-called daisy chain for priority resolution. Like the refresh register, this register has also sometimes been used creatively; in interrupt modes 0 and 1 (or in a system not using interrupts) it can be used as simply another 8-bit data register.

The instructions LD A,R and LD A,I affect the Z80 flags register, unlike all the other LD (load) instructions. The Sign (bit 7) and Zero (bit 6) flags are set according to the data loaded from the Refresh or Interrupt source registers. For both instructions, the Parity/Overflow flag (bit 2) is set according to the current state of the IFF2 flip-flop.[37]

Microarchitecture

Although the Z80 is generally considered an eight-bit CPU, it has a four-bit ALU, so calculations are done in two steps for 8-bit quantities and four steps for 16-bit quantities (such as ADD HL,DE, ADC HL,DE, etc.).[38]

Z80 assembly language

Datapoint 2200 and Intel 8008

The first Intel 8008 assembly language was based on a very simple (but systematic) syntax inherited from the Datapoint 2200 design. This original syntax was later transformed into a new, somewhat more traditional, assembly language form for this same original 8008 chip. At about the same time, the new assembly language was also extended to accommodate the additional addressing modes in the more advanced Intel 8080 chip (the 8008 and 8080 shared a language subset without being binary compatible; however, the 8008 was binary compatible with the Datapoint 2200).

In this process, the mnemonic L, for LOAD, was replaced by various abbreviations of the words LOAD, STORE and MOVE, intermixed with other symbolic letters. The mnemonic letter M, for memory (referenced by HL), was lifted out from within the instruction mnemonic to become a syntactically freestanding operand, while registers and combinations of registers became very inconsistently denoted; either by abbreviated operands (MVI D, LXI H and so on), within the instruction mnemonic itself (LDA, LHLD and so on), or both at the same time (LDAX B, STAX D and so on).

| Intel 8008 Datapoint 2200 |

Intel 8080 Intel 8085 |

Zilog Z80 | Intel 8086/ Intel 8088 |

|---|---|---|---|

| before ca. 1973 | ca. 1974 | 1976 | 1978 |

LBC

|

MOV B,C

|

LD B,C

|

MOV CH,CL

|

--

|

LDAX B

|

LD A,(BC)

|

--

|

LAM

|

MOV A,M

|

LD A,(HL)

|

MOV AL,

|

LBM

|

MOV B,M

|

LD B,(HL)

|

MOV CH,

|

--

|

STAX D

|

LD (DE),A

|

--

|

LMA

|

MOV M,A

|

LD (HL),A

|

MOV ,AL

|

LMC

|

MOV M,C

|

LD (HL),C

|

MOV ,CL

|

LDI 56

|

MVI D,56

|

LD D,56

|

MOV DL,56

|

LMI 56

|

MVI M,56

|

LD (HL),56

|

MOV byte ptr ,56

|

--

|

LDA 1234

|

LD A,(1234)

|

MOV AL,

|

--

|

STA 1234

|

LD (1234),A

|

MOV ,AL

|

--

|

--

|

LD B,(IX+56)

|

MOV CH,

|

--

|

--

|

LD (IX+56),C

|

MOV ,CL

|

--

|

--

|

LD (IY+56),78

|

MOV byte ptr ,78

|

--

|

LXI B,1234

|

LD BC,1234

|

MOV CX,1234

|

--

|

LXI H,1234

|

LD HL,1234

|

MOV BX,1234

|

--

|

SHLD 1234

|

Zdroj:https://en.wikipedia.org?pojem=NEC_μPD9002